# INTEGRATED CIRCUITS

# APPLICATION NOTE

DataSheet4U.com

AN178

Modeling the PLL

1988 Dec

DataShe

DataSheet4U.com

Philips Semiconductors

# **Modeling the PLL**

**AN178**

#### INTRODUCTION

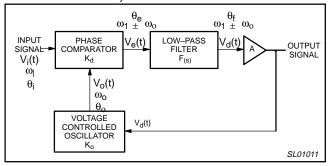

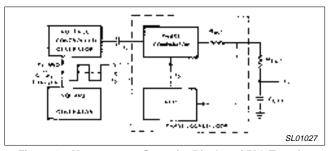

The phase-locked loop is a feedback system comprised of a phase comparator, a low-pass filter and an error amplifier in the forward signal path and a voltage-controlled oscillator (VCO) in the feedback path. The block diagram of a basic PLL system is shown in Figure 1. Perhaps the single most important point to realize when designing with the PLL is that it is a feedback system and, hence, is characterized mathematically by the same equations that apply to other, more conventional feedback systems. However, the parameters in the equations are somewhat different since the feedback error signal in the phase locked system is a phase rather than a current or voltage signal, as is usually the case in conventional feedback systems.

Figure 1. Block Diagram of Phase-Locked Loop

#### PHASE-LOCKED LOOP OPERATION

The basic principle of the PLL operation can be briefly explained as Sheet follows:

With no signal input applied to the system, the VCO control voltage  $V_d(t)$  is equal to zero. The VCO operates at a set frequency,  $f_O$ ' (or the equivalent radian frequency ωO') which is known as the free-running frequency. When an input signal is applied to the system, the phase comparator compares the phase and the frequency of the input with the VCO frequency and generates an error voltage V<sub>e</sub>(t) that is related to the phase and the frequency diHerence between the two signals. This error voltage is then filtered, amplified, and applied to the control terminal of the VCO. In this manner, the control voltage V<sub>d</sub>(t) forces the VCO frequency to vary in a direction that reduces the frequency difference between  $\omega_{O}$ and the input signal. If the input frequency  $\omega_l$  is sufficiently close to ω<sub>O</sub>, the feedback nature of the PLL causes the VCO to synchronize or lock with the incoming signal. Once in lock, the VCO frequency is identical to the input signal except for a finite phase difference.

This net phase difference of  $\theta_e$  where

$$\theta_{e} = \theta_{o} - \theta_{i} \tag{1}$$

is necessary to generate the corrective error voltage V<sub>d</sub> to shift the VCO frequency from its free-running value to the input signal frequency ω<sub>I</sub> and thus keep the PLL in lock. This selfcorrecting ability of the system also allows the PLL to track the frequency changes of the input signal once it is locked. The range of frequencies over which the PLL can maintain lock with an input signal is defined as the "lock range" of the system. The band of frequencies over which the PLL can acquire lock with an incoming signal is known as the "capture range" of the system and is never greater than the lock range.

Another means of describing the operation of the PLL is to observe that the phase comparator is in actuality a multiplier circuit that mixes the input signal with the VCO signal. This mix produces the sum and difference frequencies  $\omega_{\text{I}} \pm \omega_{\text{O}}$  shown in Figure 1. When the loop is in lock, the VCO duplicates the input frequency so that

the difference frequency component ( $(\omega_l \times \omega_O)$ ) is zero; hence, the output of the phase comparator contains only a DC component. The low-pass filter removes the sum frequency component  $(\omega_{\text{I}}+\omega_{\text{O}})$  but passes the DC component which is then amplified and fed back to the VCO. Notice that when the loop is in lock, the difference frequency component is always DC, so the lock range is independent of the band edge of the low-pass filter.

#### **LOCK AND CAPTURE**

Consider now the case where the loop is not yet in lock. The phase comparator again mixes the input and VCO signals to produce sum and difference frequency components. However, the difference component may fall outside the band edge of the low-pass filter and be removed along with the sum frequency component. If this is the case, no information is transmitted around the loop and the VCO remains at its initial free-running frequency. As the input frequency approaches that of the VCO, the frequency of the difference component decreases and approaches the band edge of the low-pass filter. Now some of the difference component is passed, which tends to drive the VCO towards the frequency of the input signal. This, in turn, decreases the frequency of the difference component and allows more information to be transmitted through the low-pass filter to the VCO. This is essentially a positive feedback mechanism which causes the VCO to snap into lock with the input signal. With this mechanism in mind, the term "capture range" can again be defined as 'the frequency range centered about the VCO initial free-running frequency over which the loop can acquire lock with the input signal'. The capture range is a measure of how close the input signal must be in frequency to that of the VCO to acquire lock. The "capture range" can assume any value within the lock range and depends primarily upon the band edge of the low-pass filter together with the closed-loop gain of the system. It is this signal capturing phenomenon which gives the loop its frequency-selective properties.

It is important to distinguish the "capture range" from the "lock range" which can, again, be defined as 'the frequency range usually centered about the VCO initial free-running frequency over which the loop can track the input signal once lock has been achieved'.

When the loop is in lock, the difference frequency component at the output of the phase comparator (error voltage) is DC and will always be passed by the low-pass filter. Thus, the lock range is limited by the range of error voltage that can be generated and the corresponding VCO frequency deviation produced. The lock range is essentially a DC parameter and is not affected by the band edge of the low-pass filter.

## THE CAPTURE TRANSIENT

The capture process is highly complex and does not lend itself to simple mathematical analysis. However, a qualitative description of the capture mechanism may be given as follows. Since frequency is the time derivative of phase, the frequency and the phase errors in the loop can be related as

$$\Delta \omega = \frac{d\theta_e}{d_t} \tag{2}$$

where  $\Delta\omega$  is the instantaneous frequency separation between the signal and VCO frequencies and  $\theta_{\mbox{\scriptsize e}}$  is the phase difference between the input signal and VCO signals.

If the feedback loop of the PLL were opened between the low-pass filter and the VCO control input, then for a given condition of  $\omega_{O}$  and  $\omega_l$  the phase comparator output would be a sinusoidal beat note at a fixed frequency  $\Delta\omega$ . If  $\omega_l$  and  $\omega_O$  were sufficiently close in

DataShe

DataSheet

et4U.com

1988 Dec

# Modeling the PLL

**AN178**

frequency, this beat note would appear at the filter output with negligible anenuation.

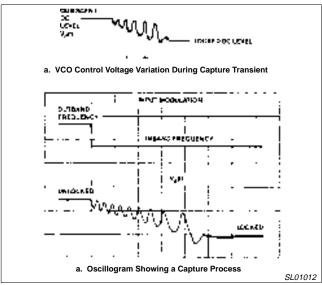

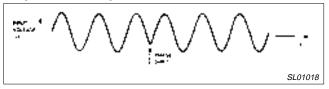

Figure 2. Asynchronous Error Beat Frequency During the Capture Transient

Now suppose that the feedback loop is closed by connecting the low-pass filter output to the VCO control terminal. The VCO frequency will be modulated by the beat note. When this happens; Sheet  $^{a}$ U  $_{\Delta \omega}$  itself will become a function of time. If, during this modulation process, the VCO frequency moves closer to b.

$$\omega_{\text{I}}$$

, (i.e., decreasing  $\Delta\omega$ ), then  $\frac{d\theta_{\text{e}}}{dt}$  decreases

and the output of the phase comparator becomes a slowly varying function of time. Similarly, if the VCO is modulated away from

$$\omega_{\text{I}}, \ \frac{d\theta_{\text{e}}}{dt}$$

increases and the error voltage

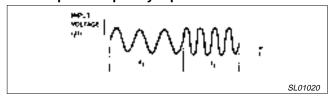

becomes a rapidly varying function of time. Under this condition the beat note waveform no longer looks sinusoidal; it looks like a series of aperiodic cusps, depicted schematically in Figure 2a. Because of its asymmetry, the beat note waveform contains a finite DC component that pushes the average value of the VCO toward  $\omega_{\rm l}$  and lock is established. When the system is in lock,  $\Delta\omega$  is equal to zero and only a steady-state DC error voltage remains.

Figure 2b displays an oscillogram of the loop error voltage  $V_d(t)$  in an actual PLL system during the capture process. Note that as lock is approached,  $\Delta \omega$  is reduced, the low-pass filter anenuation becomes less, and the amplitude of the beat note increases.

The total time taken by the PLL to establish lock is called the *pull-in time*. Pull-in time depends on the initial frequency and phase differences between the two signals as well as on the overall loop gain and the low-pass filter bandwidth. Under certain conditions, the pull-in time may be shorter than the period of the beat note and the loop can lock without an oscillatory error transient.

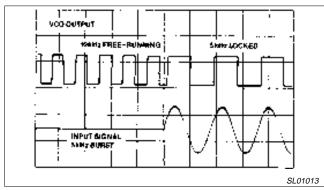

A specific case to illustrate this is shown in Figure 3. The 565 PLL is shown acquiring lock within the first cycle of the input signal. The PLL was able to capture in this short time because it was operated as a first-order loop (no low-pass filter) and the input tone-burst frequency was within its lock and capture range.

Figure 3. Exhibited by First-Order Fast Capture Transient

#### **EFFECT OF THE LOW-PASS FILTER**

In the operation of the loop, the low-pass filter serves a dual function.

First, by anenuating the high frequency error components at the output of the phase comparator, it enhances the interference-rejection characteristics; second, it provides a short-term memory for the PLL and ensures a rapid recapture of the signal if the system is thrown out of lock due to a noise transient. Decreasing the low-pass filter bandwidth has the following effects on system performance (Long Time Constant):

- The capture process becomes slower, and the pull-in time increases.

- b. The capture range decreases.

- c. Interference-rejection properties of the PLL improve since the error voltage caused by an interfering frequency is attenuated further by the low-pass filter.

- d. The transient response of the loop (the response of the PLL to sudden changes of the input frequency within the capture range) becomes underdamped.

The last effect also produces a practical limitation on the low-pass loop filter bandwidth and roll-off characteristics from a stability standpoint. These points will be explained further in the following analysis.

## MATHEMATICALLY DEFINING PLL OPERATION

As mentioned previously, the phase comparator is basically an analog multiplier that forms the product of an RF input signal,  $V_{\rm i}(t)$ , and the output signal,  $v_{\rm o}(t)$ , from the VCO. Refer to Figure 1 and assume that the two signals to be multiplied can be described by

$$V_{i}(t) = V_{i} \sin \omega_{i} t \tag{3}$$

$$V_o(t) = V_O \sin(\omega_O t) \theta_e$$

(4)

where  $\omega_l$ ,  $\omega_O$ , and  $\theta_e$  are the frequency and phase difference (or phase error) characteristics of interest. The product of these two signals is an output voltage given by

$$V_e(t) = K_1 V_1 V_0 (\sin \omega_1 t) [\sin e(\omega_0 t \theta_e)]$$

(5)

where  $K_1$  is an appropriate dimensional constant. Note that the amplitude of  $v_e(t)$  is directly proportional to the amplitude of the input signal  $V_l$ . The two cases of an unlocked loop  $(\omega_l \neq \omega_O)$  are now considered separately.

et4U.com

DataShe

DataSheet

# Modeling the PLL

**AN178**

DataShe

## Unlocked State ( $\omega_l \neq \omega_O$ )

When the two frequencies to the phase comparator are not synchronized, the loop is not locked. Furthermore, the phase angle difference  $\theta_e$  in Equations 4 and 5 is meaningless lor this case since it can be eliminated by appropriately choosing the time origin.

Using trigonometric identities, Equation 5 can be rewritten as

$$v_{e}(t) = \frac{K_{1}V_{1}V_{0}}{2} [\cos(\omega_{1} - \omega_{0})t - \cos(\omega_{1} - \omega_{0})t]$$

(6)

When  $v_e(t)$  is passed through the low-pass filter, F(s), the sum frequency component is removed, leaving

$$v_{f}(t) = K_{2}V_{I}V_{O} \cos (\omega_{I} - \omega_{O})t$$

(7)

where  $\mathrm{K}_2$  is a constant. After amplification, the control voltage for the VCO appears as

$$v_{d}(t) = AK_{2}V_{1}V_{O} \cos (\omega_{1} - \omega_{O})t$$

(8)

This equation shows that a beat frequency effect is established between  $\omega_l$  and  $\omega_O$ , causing the VCO's frequency to deviate by  $\pm\Delta\omega$  from  $\omega_O$ ' in proportion to the signal amplitude (AK $_2$ V $_l$ V $_O$ ) passing through the filter. If the amplitude of V $_l$  is sufficiently large and if signal limiting or saturation does not occur, the VCO output frequency will be shifted from  $\omega_O$ ' by some  $\Delta\omega$  until lock is established where

$$\omega_{l} = \omega_{O} = \omega_{O} \pm \Delta \omega \tag{9}$$

If lock cannot be established, then either  $V_l$  is too small to drive the Sheef VCO to produce the necessary  $\pm\Delta\omega$  deviation or  $\omega_l$  is beyond the dynamic range of the VCO, i.e.,  $\omega_l >< \omega_O' \pm \Delta\omega$ . Remedies for these no lock conditions are:

- Increase VI either internally or externally to the loop by providing additional amplification.

- Increase the internal loop gain by adjusting upward (larger -3dB frequency) the response of the low-pass filter.

- 3. Shift  $\omega_O$ ' closer to the expected  $\omega_I$ . Establishing frequency lock leads to the second case where  $\omega_I = \omega_O$ .

## Locked State ( $\omega_I = \omega_O$ )

When  $\omega_l$  and  $\omega_O$  are frequency synchronized, the output signal from the phase comparator for  $\omega_l = \omega_O = \omega$  and a phase shift of  $\theta_e$  is

$$v_{e}(t) = K_{1}V_{1}V_{0}(\sin\omega t) \sin (\omega t \quad \theta_{e})$$

$$= \frac{K_{1}V_{1}V_{0}}{2}[\cos\theta_{e} - \cos (2\omega t \quad \theta_{e})]$$

(10)

The low-pass filter removes the high frequency, AC component of  $v_e(t)$ , leaving only the DC component. Thus,

$$v_{f}(t) = K_{2}V_{I}V_{O}\cos\theta_{e}$$

(11)

After amplification the DC voltage driving the VCO and maintaining lock within the loop is

$$v_{d}(t) = V_{D} = AK_{2}V_{1}V_{O}\cos\theta_{e}$$

(12)

Suppose  $\omega_l$  and  $\omega_O$  are perfectly synchronized to the free-running frequency  $\omega_O$ '. For this case,  $V_D$  will be zero, indicating that  $\theta_e$  must be  $\pm 90^\circ$ . Thus  $V_D$  is proportional to the phase difference or phase error between  $\theta_l$  and  $\theta_o$  centered about a reference phase angle of  $\pm 90^\circ$ . If  $\omega_l$  changes slightly from  $\omega_O$ ', the first effect will be a change in  $\theta_e$  from  $\pm 90^\circ$ .  $V_D$  will adjust and settle out to some non-zero value to correct  $\omega_O$ ; under this condition frequency lock is maintained with  $\omega_l = \omega_O$ . The phase error will be shifted by some

amount  $\Delta\theta$  from the reference phase angle of  $\pm90^\circ.$  This concept can be simplified by redefining  $\theta_e$  as

$$\theta_{e} = \theta_{f} \pm \Delta\theta \tag{13}$$

where  $\theta_n$  is the inherent, reference phase shift of  $\pm 90^\circ$  and  $\Delta\theta$  is the departure from this reference value. Now the VCO control voltage becomes

$$v_{D} = AK_{1}V_{1}V_{O}\cos(\theta_{r} \pm \Delta\theta)$$

$$= \pm AK_{2}v_{1}V_{O}\sin\Delta\theta$$

(14)

Since the sine function is odd, a momentary change in  $\Delta\theta$  contains information about which way to adjust the VCO frequency to correct and maintain the locked condition. The maximum range over which  $\Delta\theta$  changes can be tracked is -90° to +90°. This corresponds to a  $\theta_e$  range from 0 to 180°.

In addition to being an error signal,  $V_D$  represents the demodulated output of an FM input applied as  $v_{in}(t)$  assuming a linear VCO characteristic. Thus, FM demodulation can be accomplished with the PLL without the inductively-tuned circuits that are employed with conventional detectors.

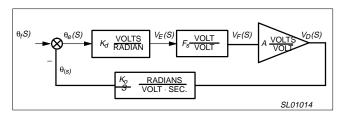

## **DETERMINING PLL MODEL PARAMETERS**

Since the PLL is basically an electronic servo loop, many of the analytical techniques developed for control systems are applicable to phase-locked systems. Whenever phase lock is established between  $v_i(t)$  and  $v_o(t)$  the linear model of Figure 4 can be used to predict the performance of the PLL system. Here  $\theta_i$  and  $\theta_o$  represent the phase angles associated with the input/output waveshapes, respectively; F(s) represents a generalized voltage transfer function for the low-pass filter in the s complex frequency domain; and  $K_d$  and  $K_o$  are conversion gains of the phase comparator and VCO, respectively, each having units as shown. The 1/s term associated with the VCO accounts for the inherent  $90^\circ$  phase shift in the loop since the VCO converts a voltage to a frequency and since phase is the integral of frequency. Thus the VCO functions as an integrator in the feedback loop.

Figure 4. Linear Model of PLL System

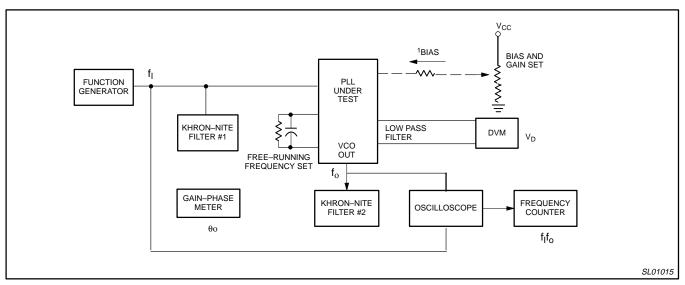

Specific values of  $K_d$  and  $K_0$  for all of Philips Semiconductors general purpose PLLs can be found in the sections describing the particular loop of interest. However, sometimes it may be desired to determine these conversion gains exactly for a specific device. The measurement scheme shown in Figure 5 can be used to determine  $K_d$  and Ko for a loop under lock. The function of the Khron-Hite filters is to extract the fundamental sinusoidal frequency component of their square wave inputs for application to the Gain-Phase Meter. If the input signal from the Function Generator is sinusoidal, then the first Khron-Hite filter may be eliminated. It is recommended to use high impedance oscilloscope probes so as to not distort the input of VCO waveshapes, thereby potentially altering their phase relationships. The frequency counter can be driven from the scope as shown, or connected directly to the input or VCO, provided as Sheet 4U.com input impedance is large.

et4U.com

DataS

DataOnco

1988 Dec

# Modeling the PLL

**AN178**

Figure 5. Measurement Scheme for K<sub>d</sub> and K<sub>o</sub> Determinations

The procedure to follow for obtaining  $K_d$  and  $K_o$  is as follows:

- Establish the desired external bias and gain conditions for the PLL under test.

- With the Function Generator turned off, set the free-running frequency of the loop via the timing capacitor and timing resistors heet 4U.cko(horm) = Ko rad if appropriate. Monitor fo' with the Frequency Counter.

- Turn on the Function Generator and check to make sure the amplitude of the input signal is appropriate for the particular loop under test.

- 4. Adjust the input frequency for lock. Lock is discernable on a dual-trace scope when the input and VCO waveforms are synchronized and stationary with respect to each other. One should be especially careful to check that locking has not occurred between the VCO and some harmonic frequency. Carefully inspect both waveshapes, making sure each has the same period. (If a second Frequency Counter is available, an alternate scheme can be used to confirm frequency locking. One frequency counter is used to monitor the input signal frequency, and the second counter is used for the VCO frequency. When the two counters display the same frequency, the PLL is locked.)

- 5. Set the input frequency to the free-running frequency and note the Gain-Phase Meter display. It should be approximately 90°  $\pm 10^\circ$  nominally. Record the phase error,  $\theta_e$ , the VCO control voltage,  $V_D$ , and the input frequency,  $f_I$ .

- Adjust f<sub>I</sub> for frequencies above and below f<sub>O</sub>' and record θ<sub>e</sub> and V<sub>D</sub> for each f<sub>I</sub>, as appropriate.

- 7. Making a plot of  $V_D$  versus  $\theta_e$  is useful for checking the measurement data and the system's linearity. The slope of this plot  $(\Delta V_D/\Delta \theta_e)$  is  $K_d$  in units of  $V/^\circ$ . Multiplying this slope by  $180/\pi$  gives the desired  $K_d$  in volts/radian.

- 8. A plot of  $f_I = f_O$  versus  $V_D$  while the loop remains locked will check the VCO linearity. The slope of this plot is  $K_O$  at the particular free-running frequency. The units of slope taken directly from the graph are Hz/V. Multiplying this slope figure by  $2\pi$  gives the desired  $K_O$  in units of radians/ volt-sec.

$K_d$  is generally constant over wide frequency ranges, but is linearily related to the input signal amplitude.  $K_o$  is constant with input signal level but does vary linearily with  $f_O$ '. Often it is convenient to specify a normalized  $K_o$  as

$$4U.CK_{O(\text{norm})} = \frac{^{N}_{O}}{f_{O}} \frac{\text{rad}}{V}$$

(15)

The  $K_0$  value at any desired free-running frequency then can be estimated as

$$K_O$$

(@ any% $f_O$ ) =  $K_{O(norm)}f_O$  (16)

AThe loop gain for the PLL system is

$$K_{v} = K_{d}K_{o}A \tag{17}$$

(Often when the gain A is due to an amplifier internal to the IC, A will be included in either  $K_d$  or  $K_o$ . This is further illustrated in the article on the 565 PLL.)

# MODELING THE PLL SYSTEM WITH VARIOUS LOW-PASS FILTERS

The open-loop transfer function for the PLL is

$$T(s) = \frac{K_V F(s)}{s} \tag{18}$$

Using linear feedback analysis techniques, and assuming that the VCO is in the forward path, the closed-loop transfer characteristics H(s) can be related to the open-loop performance as

$$H(s) = \frac{T(s)}{1 - T(s)} \tag{19}$$

and the roots of the characteristic system polynomial can be readily determined by root-locus techniques.

From these equations, it is apparent that the transient performance and frequency response of the loop is heavily dependent upon the choice of filter and its corresponding transfer characteristic, F(s).

www.DataSheet4U.com

DataShe

et4U.com

.....batasneet+e.ee

# Modeling the PLL

**AN178**

DataShe

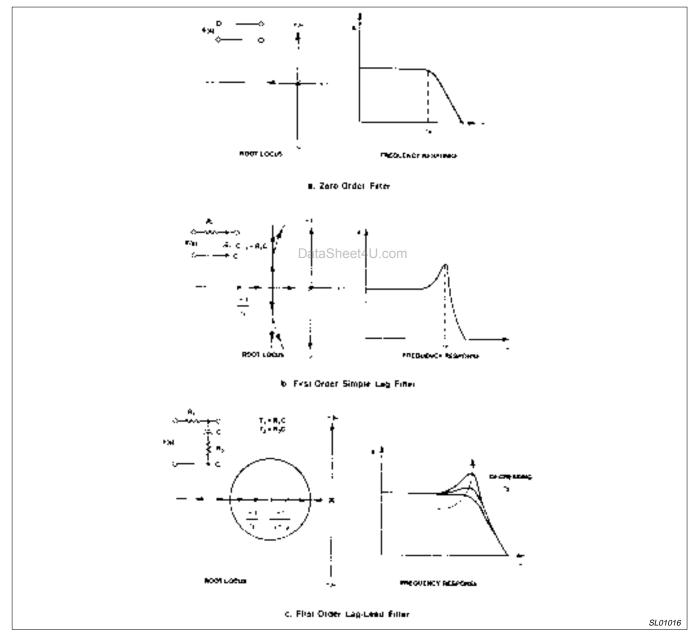

## Zero-Order Filter — F(s) = 1

The simplest case is that of the first-order loop where F(s)=1 (no filter). The closed-loop transfer function then becomes

$$H(s) = \frac{K_V}{S K_V}$$

(20)

This transfer function gives the root locus as a function of the total loop gain  $K_{\nu}$  and the corresponding frequency response shown in

Figure 6a. The open-loop pole at the origin is due to the integrating action of the VCO. Note that the frequency response is actually the amplitude of the difference frequency component versus modulating frequency when the PLL is used to track a frequency-modulated input signal. Since there is no low-pass filter in this case, sum frequency components are also present at the phase comparator output and must be filtered outside of the loop if the difference frequency component (demodulated FM) is to be measured.

Figure 6. Root Locus and Frequency Response Plots

DataSheet4U.com www.DataSheet4U.com

1988 Dec 6 DataSheet4U.com

DataSheet4U.com

# Modeling the PLL

**AN178**

DataShe

#### First-Order Filter

With the addition of a single-pole low-pass filter F(s) of the form

$$F(s) = \frac{1}{1 + s}$$

(21)

where  $\tau 1 = R_1C_1$ , the PLL becomes a second-order system with the root locus shown in Figure 6b. Again, an open-loop pole is located at the origin because of the integrating action of the VCO. Another open-loop pole is positioned on the real axis at  $-1/\tau_1$  where  $\tau_1$  is the time constant of the low-pass filter.

One can make the following observations from the root locus characteristics of Figure 6b:

- a. As the loop gain  $K_{\text{V}}$  increases for a given choice of  $\tau_{\text{1}},$  the imaginary part of the closed-loop poles increases: thus, the natural frequency of the loop increases and the loop becomes more and more under-damped.

- b. If the filter time constant is increased, the real part of the closed-loop poles becomes smaller and the loop damping is

As in any practical feedback system, excess shifts or non-dominant poles associated with the blocks within the PLL can cause the root loci to bend toward the right half plane as shown by the dashed line in Figure 6b. This is likely to happen if either the loop gain or the filter time constant is too large and may cause the loop to break into sustained oscillations.

## First-Order Lag-Lead Filter

et4U.com

The stability problem can be eliminated by using a lag-lead type of filter, as indicated in Figure 6c. This type of a filter has the transfer lock range. For the simple first-order lag filter function

$$F(s) = \frac{1}{1} \frac{2^{s}}{(tau_{1} + 2)^{s}}$$

(22)

where  $\tau_2 = R_2C$  and  $\tau_1 = R_1C$ . By proper choice of  $R_2$ , this type of filter confines the root locus to the left half-plane and ensures stability. The lag-lead filter gives a frequency response dependent on the damping, which can now be controlled by the proper adjustment of  $\tau_1$  and  $\tau_2$ . In practice, this type of filter is important because it allows the loop to be used with a response between that of the firstand second-order loops and it provides an additional control over the loop transient response. If  $R_2 = 0$ , the loop behaves as a second-order loop and as  $R_2 \rightarrow \infty$ , the loop behaves as a first-order loop due to a pole-zero cancellation. However, as first-order operation is approached, the noise bandwidth increases and interference rejection decreases since the high frequency error components in the loop are now attenuated to a lesser degree.

## Second- and Higher-Order Filters

Second- and higher-order filters, as well as active filters, occasionally are designed and incorporated within the PLL to achieve a particular response not possible or easily obtained with zero or first-order filters. Adding more poles and more gain to the closedloop transfer function reduces the inherent stability of the loop. Thus the designer must exercise extreme care and utilize complex stability analysis if second-order (and higher) filters or active filters are to be considered.

#### CALCULATING LOCK AND CAPTURE RANGES

In terms of the basic gain expression in the and system, the lock range of the PLL  $\omega_1$  can be shown to be numerically equal to the DC loop gain (2-sided lock range).

$$2\omega_{\perp}$$

4 f<sub>\(\pri} K<sub>\(\psi\)</sub>F(0) (23)</sub>

where F(O) is the value of the low-pass filters transfer function at

Since the capture range  $\omega_{C}$  denotes a transient condition, it is not as readily derived as the lock range. However, an approximate expression for the capture range can be wrinen as (2-sided capture

$$2\omega_{C} = 4 f_{C} K_{V} | F(i\omega_{C}) |$$

(24)

where  $F(i\omega_C)$  is the magnitude of the low-pass filter transfer function evaluated at  $\omega_{\text{C}}$ . Solution of Equation 24 frequently involves a "trial and error" process since the capture range is a function of itself. Note that at all times the capture range is smaller than the lock rage. For the simple first-order lag filter of Figure 6b, the capture range can be approximated as

$$2\omega_{c} \quad 2 \quad \frac{\overline{\omega_{L}}}{1} = 2 \quad \frac{\overline{K_{V}}}{1} \tag{25}$$

This approximation is valid for

$$_{1} \quad \frac{1}{2\omega_{\mathsf{L}}} \tag{26}$$

Equations 23 and 24 show that the capture range increases as the low-pass filter time constant is decreased, whereas the lock range is unaffected by the filter and is determined solely by the loop gain.

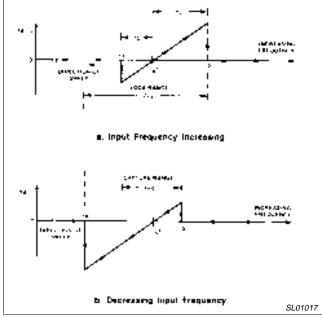

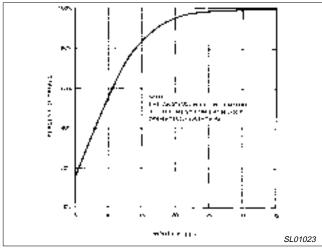

Figure 7. Typical PLL Frequency-to-Voltage Transfer Characteristics

www.DataSheet4U.com

## Modeling the PLL

AN178

Figure 7 shows the typical frequency-to-voltage transfer characteristics of the PLL. The input is assumed to be a sine wave whose frequency is swept slowly over a broad frequency range. The vertical scale is the corresponding loop error voltage. In Figure 7a, the input frequency is being gradually increased. The loop does not respond to the signal until it reaches a frequency ω<sub>1</sub>, corresponding to the lower edge of the capture range. Then, the loop suddenly locks on the input and causes a negative jump of the loop error voltage. Next, V<sub>d</sub> varies with frequency with a slope equal to the reciprocal of VCO conversion gain (1/Ko) and goes through zero as  $\omega_I = \omega_O'$ . The loop tracks the input until the input frequency reaches ω<sub>2</sub>, corresponding to the upper edge of the lock range. The PLL then loses lock and the error voltage drops to zero. If the input frequency is swept slowly back, the cycle repeats itself, but is inverted, as shown in Figure 7b. The loop recaptures the signal at  $\omega_3$  and tracks it down to  $\omega_4.$  The total capture and lock ranges of the system are:

$$2\omega_{C} = \omega_{3} - \omega_{1} \tag{27}$$

and

$$2\omega_{L} = \omega_{2} - \omega_{4} \tag{28}$$

Note that, as indicated by the transfer characteristics of Figure 7, the PLL system has an inherent selectivity about the free-running frequency,  $\omega_{\Omega}$ . It will respond only to the input signal frequencies that are separated from  $\omega_{O}$  by less than  $\omega_{C}$  or  $\omega_{L}$ , depending on whether the loop starts with or without an initial lock condition. The linearity of the frequency-to-voltage conversion characteristics for Sheet the PLL is determined solely by the VCO conversion gain. Therefore, in most PLL applications, the VCO is required to have a

highly linear voltage-to-frequency transfer characteristic.

#### **DETERMINING LOOP RESPONSE**

The transient response of a PLL can be calculated using the model of Figure 4 and Equations 18 and 19 as starting points. Combining these equations gives

$$H(s) = \frac{\theta_o(s)}{\theta_i(s)} = \frac{K_V F(s)}{s K_V F(s)}$$

(29)

The phase error which keeps the system in lock is

$$\theta_{e}(s) = \theta_{i}(s) - \theta_{o}(s) \tag{30}$$

Define a phase error transfer function

$$E(s) \qquad \frac{\theta_{e}(s)}{\theta_{i}(s)} = 1 - \frac{\theta_{o}(s)}{\theta_{i}(s)} = 1 - H(s)$$

(31)

As an example of the utilization of these equations, consider the most common case of a loop employing a simple first-order lag filter where

$$F(s) = \frac{1}{1 - s} \tag{32}$$

For this filter, Equations 29 and 31 become

$$H(s) = \frac{K_{V-1}}{s - s_{-1} - K_{V-1}}$$

(33)

DataSheet4U.com =

$$\frac{s(s \quad 1 \quad 1)}{s \quad s \quad 1 \quad K_{V \quad 1}}$$

(34)

Both equations are second-order and have the same denominator which can be expressed as

$$D(s) = s^2 \quad s \quad K_{V 1} = s^2 \quad 2 \omega_n s \quad \omega_n^2$$

(35)

Where  $\omega_n$  and  $\zeta$  are, respectively, the system's undamped natural frequency and damping factor defined as

$$\omega_{\mathsf{n}} = \overline{\mathsf{K}_{\mathsf{V}-1}} \tag{36}$$

$$= \frac{1}{K_{V,1}} = \frac{\omega_n}{2K_V}$$

(37)

The system is considered overdamped for  $\zeta > 1.0$ , and critically damped  $\zeta$  = 1.0. Now examine this PLL system's response to various types of inputs.

## Step-of-Phase Input

Figure 8. Input Signal Representing a Unit Step of Phase at **Constant Frequency**

Consider a unit step-of-phase as the input signal. This input is shown in Figure 8 and can be thought of as simply shifting the time axis by a unit step (one radian or one degree, depending upon the working units) while maintaining the same input frequency. Mathematically this input has the form

$$\theta_{i}(s) = \frac{1}{s} \tag{38}$$

The phase of VCO output and the system's phase error are

$$\theta_{o}(s) = \frac{H(s)}{s} = \frac{\omega_{n}^{2}}{s(s^{2} - 2\omega_{n}s - \omega_{n}^{2})}$$

(39)

$$\theta_{0}(s) = \frac{E(s)}{s} = \frac{s + 2\omega_{n}}{s^{2} + 2\omega_{n}s + \omega_{n}^{2}}$$

(40)

(depending upon the working units) while maintaining the same input frequency. Mathematically this input has the form

$$\theta_{o}(t) = 1 \qquad \frac{e - \omega_{n}t}{1 - \frac{2}{2}} \sin \left(\omega_{n}t - \frac{1}{1 - \frac{2}{2}}\right) \tag{41}$$

where =

$$\arctan \frac{1-2}{1-2}$$

(42)

and  $\zeta \neq 1$ .

$$\theta_{e}(t) = \frac{e - \omega_{n}(t)}{1 - 2} \sin(\omega_{n}t \frac{1 - 2}{1 - 2})$$

(43)

When  $\zeta = 1$ , these phase responses are

$$\theta_{o}(t) = 1 - (1 - \omega_{n}t)e - \omega_{n}t$$

(44)

$$\theta_e(t) = (1 \quad \omega_n t)e - \omega_n t$$

(45)

www.DataSheet4U.com

DataShe

# Modeling the PLL

**AN178**

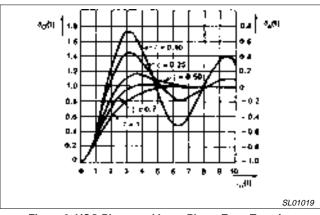

Figure 9. VCO Phase and Loop Phase Error Transient Responses for Various Damping Factors

Figure 9 is a plot of the VCO phase response and the phase error transient for various damping factors. Note from this figure that an underdamped system has overshoot which can cause the loop to break lock if this overshoot is too large. The critical condition for maintaining lock is to keep the phase error within the dynamic range for the phase comparator of  $-\pi/2$  to  $\pi/2$  radians. For the underdamped case, the peak phase-error overshoot is

$$\theta_{e}(\text{max}) = e - \frac{1}{1 - 2} \tag{46}$$

which must be less than  $\pi/2$  to maintain lock. Lock can also be broken for the overdamped and critically-damped loops if the input phase shift is too large where the phase error exceeds  $\pm \pi/2$  radians.

The analysis and equations given are based upon the small-signal model of Figure 4. If the signal amplitudes become too large, one or more functional blocks in the system can saturate, causing a slew rate type limiting action that may break lock.

The *transient change* in the VCO frequency due to the unit step-of-phase input can be found by taking the time derivative of Equation 41 or alternatively by finding the inverse Laplace transform of

$$\omega_{o}(s) = s\theta_{o}(s) = \frac{\omega_{n}^{2}}{s^{2} + 2 \omega_{n}s + \omega_{n}^{2}}$$

(47)

which is

$$\omega_{O}(t) = \frac{\omega_{n}e - \omega_{n}t}{1 - \frac{2}{2}} \sin \omega_{n}t \frac{1}{1 - \frac{2}{2}}$$

(48)

#### Unit Step-of-Frequency Input

Figure 10. Input Signal for a Unit Step-of-Frequency at Constant Phase

This type of input occurs when the input frequency is DataSheet4hstantaneously changed from one frequency to another as is done

in FSK and modem applications. For this input, as shown in Figure 10,

$$\theta_{i}(s) = \frac{1}{s^{2}} \tag{49}$$

The VCO output phase is

$$\theta_{o}(s) = \frac{\omega_{n}^{2}}{s^{2}(s^{2} + 2\omega_{n}s + \omega_{n}^{2})}$$

(50)

The time expression for the VCO phase change is

$$\theta_{o}(t) = t - \frac{2}{\omega_{n}}$$

$\frac{e - \omega_{n}t}{\omega_{n} \frac{1}{1 - \omega^{2}}} \sin(\omega_{n}t) \frac{1 - \omega^{2}}{1 - \omega^{2}}$  (51)

for  $\zeta \neq 1$ .

The time expression for the VCO frequency change for a unit step-of-frequency input is the same as the time response VCO phase change due to a step-of-phase input (Equation 41), or

$\omega_O(t)$  for frequency step input =  $\theta_O(t)$  for phase step input. Thus

$$\omega_{o}(t) = 1 \qquad \frac{e - \omega_{n}t}{1 - 2} \sin(\omega_{n}t) \frac{1 - 2}{1 - 2}$$

(52)

for  $\zeta \neq 1$ .

## **Unit Ramp-of-Frequency Input**

Figure 11. Input Signal for a Unit Ramp-of-Frequency Input

This form of input signal represents sweeping the input frequency at a constant rate and direction as shown in Figure 11. The amplitude and phase of the input remain constant; the input frequency changes linearly with time. Since the input signal to the PLL model is a phase, a unit ramp-of-frequency appears as a phase acceleration type input that can be mathematically described as

$$\theta_{i}(s) = \frac{1}{s^{3}} \tag{53}$$

The VCO output phase change is

$$\theta_{o}(s) = \frac{\omega_{n}^{2}}{s^{3}(s^{2} + 2\omega_{n}s + \omega_{n}^{2})}$$

(54)

The time expression for the VCO phase change is

$$\theta_{o}(s) = \frac{t^{2}}{2} - \frac{2t}{\omega_{n}} \frac{2}{\omega_{n}^{2}} \left[ 2(1 - \omega_{n}^{2}) - \frac{1 - 4^{2}\omega_{n}^{2}}{1 - 2^{2}} \right]$$

$$(55)$$

$$x e^{-\omega n^t} sin(\omega_n t \overline{1 - 2})$$

where = arc tan

$$\frac{1 - 2}{(1 - 2\omega_n^2)^2}$$

and y is given in Equation 42.

www.DataSheet4U.com

DataShe

# Modeling the PLL

## **AN178**

#### PLL BUILDING BLOCKS VCO

Since three different forms of VCO have been used in the Philips Semiconductors PLL series, the VCO details will not be discussed until the individual loops are described. However, a few general comments about VCOs are in order.

When the PLL is locked to a signal, the VCO voltage is a function of the frequency of the input signal. Since the VCO control voltage is the demodulated output during FM demodulation, it is important that the VCO voltage-to-frequency characteristic be linear so that the output is not distorted. Over the linear range of the VCO, the conversin gain is given by  $K_{\mbox{\scriptsize O}}$  (in radian/V-sec)

$$K_{O} = \frac{\Delta \omega_{O}}{\Delta V_{d}} \tag{56}$$

Since the loop output voltage is the VCO voltage, we can get the loop output voltage as

$$\Delta V_{d} = \frac{\Delta \omega_{O}}{K_{O}} \tag{57}$$

The gain  $K_O$  can be found from the data sheet. When the VCO voltage is changed, the frequency change is virtually instantaneous.

## **Phase Comparator**

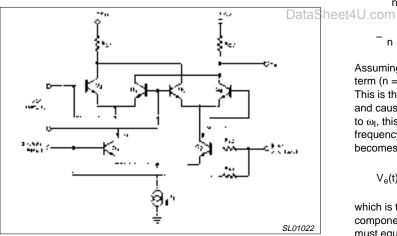

All of Philips Semiconductors analog phase-locked loops use the same form of phase comparator — often called the doubly-balanced multiplier or mixer. Such a circuit is shown in Figure 12.

Figure 12. Integrated Phase Comparator Circuit

The input stage formed by transistors Q1 and Q2 may be viewed as a differential amplifier which has an equivalent collector resistance

$R_C$  and whose differential gain at balance is the ratio of  $R_C$  to the dynamic emitter resistance,  $r_e$ , of Q1 and Q2.

$$A_{d} = \frac{R_{C}}{r_{e}} = \frac{\frac{R_{C}}{0.026}}{I_{E} 2} = \frac{R_{C}I_{E}}{0.052}$$

(58)

where  $I_{\mbox{\scriptsize E}}$  is the total DC bias current for the differential amplifier pair.

The switching stage formed by Q3 – Q6 is switched on and off by the VCO square wave. Since the collector current swing of Q2 is the negative of the collector current swing of Q1, the switching action has the effect of multiplying the differential stage output first by +1 and then by –1. That is, when the base of Q4 is positive,  $R_{C2}$  receives  $I_1$  and when the base of Q6 is positive,  $R_{C2}$  receives  $i_2$  =  $i_1$ .

Since the circuit is called a multiplier, performing the multiplication will gain further insight into the action of the phase comparator.

Consider an input signal which consists of two added components: a component at frequency  $\omega_I$  which is close to the free-running frequency and a component at frequency  $\omega_K$  which may be at any frequency. The input signal is

$$v_i(t)$$

$v_k(t) = V_1 \sin(\omega_i t + \theta_i) + v_k \sin(\omega_k t + \omega_k)$  (59)

where  $\theta_i$  and  $\theta_k$  are the phase in relation to the VCO signal. The unity square wave developed in the multiplier by the VCO signal is

$$v_o(t) = n = 0 \frac{4}{(2n - 1)} \sin[(2n - 1)\omega_o t]$$

(60)

where  $\omega_O$  is the VCO frequency. Multiplying the two terms, using the appropriate trigonometric relationships, and inserting the differential stage gain  $A_d$  gives:

$- \frac{V_k}{n = 0} \frac{(2n - 1)}{(2n - 1)} \cos[(2n - 1) \omega_0 t - \omega_1 t - \theta_1] ]$

Assuming that temporarily  $V_k$  is zero, if  $\omega_l$  is close to  $\omega_O$ , the first term (n = 0) has a low frequency difference frequency component. This is the beat frequency component that feeds around the loop and causes lock-up by modulating the VCO. As  $\omega_O$  is driven closer to  $\omega_l$ , this difference component becomes lower and lower in frequency until  $\omega_O = \omega_l$  and lock is achieved. The first term then becomes

$$V_{e}(t) = V_{E} = \frac{2A_{d}V_{I}}{(2n-1)}\cos\theta_{i}$$

(62)

which is the usual phase comparator formula showing the DC component of the phase comparator during lock. This component must equal the voltage necessary to keep the VCO at  $\omega_O$ . It is possible for  $\omega_O$  to equal  $\omega_I$  momentarily during the lock-up process and, yet, for the phase to be incorrect so that  $\omega_O$  passes through  $\omega_I$  without lock being achieved. This explains why lock is usually not achieved instantaneously, even when  $\omega_I=\omega_O$  at t=0.

If  $n \neq 0$  in the first term, the loop can lock when  $\omega_I = (2n + 1)\omega_O$ , giving the DC phase comparator component

$$V_{e}(t) = V_{E} = \frac{2A_{d}V_{I}}{(2n-1)}\cos\theta_{i}$$

(63)

showing that the loop can lock to odd harmonics of the free-running frequency. The (2n + 1) term in the denominator shows that the phase comparator's output is lower for harmonic lock, which explains why the lock range decreases as higher and higher odd harmonics are used to achieve lock.

Note also that the phase comparator's output during lock is DataSheet 4U.com (assuming  $A_d$  is constant) also a function of the input amplitude  $V_l$ .

DataShe

DataShee

# Modeling the PLL

**AN178**

DataShe

Thus, for a given DC phase comparator output V<sub>F</sub>, an input amplitude decrease must be accompanied by a phase change. Since the loop can remain locked only for  $\theta_i$  between 0 and 180°, the lower V<sub>I</sub> becomes, the more the lock range is reduced.

Note from the second term that during lock the lowest possible frequency is  $\omega_0 + \omega_1 = 2\omega_1$ . A sum frequency component is always present at the phase comparator output. This component is usually greatly attenuated by the low-pass filter capacitor connected to the phase comparator output. However, when rapid tracking is required (as with high-speed FM detection or FSK), the requirement for a relatively high frequency cutoff in the low-pass filter may leave this component unattenuated to the extent that it interferes with detection. At the very least, additional filtering may be required to remove this component. Components caused by n ≠ 0 in the second term are both attenuated and of much higher frequency, so they may be neglected.

Suppose that other frequencies represented by V<sub>k</sub> are present. What is their effect for  $V_k \neq 0$ ?

The third term shows that V<sub>k</sub> introduces another difference frequency component. Obviously, if  $\omega_k$  is close to  $\omega_l$ , it can interfere with the locking process since it may form a beat frequency of the same magnitude as the desired locking beat frequency. However, suppose lock has been achieved so that  $\omega_{O} = \omega_{I}$ . In order for lock to be maintained, the average phase comparator output must be constant. If  $\omega_O = \omega_k$  is relatively low in frequency, the phase  $\theta_i$  must change to compensate for this beat frequency. Broadly speaking, any signal in addition to the signal to which the loop is locked causes a phase variation. Usually this is negligible since  $\omega_k$  is often heet far removed from  $\omega_l$ . However, it has been stated that the phase  $\theta_i$ can move only between 0 and 180°. Suppose the phase limit has been reached and V<sub>k</sub> appears. Since it cannot be compensated for, it will drive the loop out of lock. This explains why extraneous signals can result in a decrease in the lock range. If V<sub>k</sub> is assumed to be an instantaneous noise component, the same effect occurs. When the full swing of the loop is being utilized, noise will decrease the lock or tracking range. This effect can be reduced by decreasing the cutoff frequency of the lowpass filter so that the  $\omega_{O} - \omega_{k}$  is attenuated to a greater extent, which illustrates that noise immunity and out-band frequency rejection is improved (at the expense of capture range since  $\omega_O - \omega_I$  is likewise attenuated when the low-pass filter capacitor is large.

The third term can have a DC component when  $\omega_k$  is an odd harmonic of the locked frequency so that  $(2n + 1) (\omega_{0} - \omega_{1})$  is zero and  $\theta_k$  makes its appearance. This will have an effect on  $\theta_1$  which will change the  $\theta_1$  versus frequency  $\omega_l$ . This is most noticeable when the waveform of the incoming signal is, for example, a square wave. The  $\theta_k$  term will combine with the  $\theta_1$  term so that the phase is a linear function of input frequency. Other waveforms will give different phase versus frequency functions. When the input amplitude V<sub>I</sub> is large and the loop gain is large, the phase will be close to 90° throughout the range of VCO swing, so this effect is

The fourth term is of little consequence except that if  $\omega_k$  approaches zero, the phase comparator output will have a component at the locked frequency  $\omega_O$  at the output. For example, a DC offset at the input differential stage will appear as a square wave of fundamental  $\omega_{\mbox{\scriptsize O}}$  at the phase comparator output. This is usually small and well attenuated by the low-pass filter. Since many out-band signals or noise components may be present, many V<sub>k</sub> terms may be DataSheet4combining to influence locking and phase during lock. Fortunately, only those close to the locked frequency need be considered.

#### Quadrature-Phase Detector (QPD)

The quadrature-phase detector action is exactly the same except that its output is proportional to the sine of the phase angle. When the phase  $\theta_i$  is 90°, the quadrature phase detector output is then at its maximum, which explains why it makes a useful lock or amplitude detector. The output of the quadrature-phase detector is given by

$$V_{q} = \frac{2A_{q}V_{l}}{\sin\theta_{i}}$$

(64)

where  $V_I$  is the constant or modulated AM signal and  $\theta_i \approx 90^\circ$  in most cases so that sine  $\theta_i = 1$  and

$$V_{q} = \frac{2A_{q}V_{l}}{} \tag{65}$$

This is the demodulation principle of the autodyne receiver and the basis for the 567 tone decoder operation.

#### **INITIAL PLL SETUP CHOICES**

In a given application, maximum PLL effectiveness can be achieved if the designer understands the tradeoffs which can be made. Generally speaking, the designer is free to select the frequency, lock range, capture range, and input amplitude.

#### FREE-RUNNING FREOUENCY SELECTION

Setting the center or free-running frequency is accomplished by selecting one or two external components. The center frequency is usually set in the center of the expected input frequency range. Since the loop's ability to capture is a function of the difference between the incoming and free-running frequencies, the band edges of the capture range are always an equal distance (in Hz) from the center frequency. Typically, the lock range is also centered about the free-running frequency. Occasionally, the center frequency is chosen to be offset from the incoming frequency so that the tracking range is limited on one side. This permits rejection of an adjacent higher or lower frequency signal without paying the penalty for narrow-band operation (reduced tracking speed).

All of Philips Semiconductors loops use a phase comparator in which the input signal is multiplied by a unity square wave at the VCO frequency. The odd harmonics present in the square wave permit the loop to lock to input signals at these odd harmonics. Thus, the center frequency may be set to, say, 1/3 or 1/5 of the input signal. The tracking range, however, will be considerably reduced as the higher harmonics are utilized.

The foregoing phase comparator discussion would suggest that the PLL cannot lock to subharmonics because the phase comparator cannot produce a DC component if  $\omega_I$  is less than  $\omega_O$ .

The loop can lock to both odd harmonic and subharmonic signals in practice because such signals often contain harmonic components at  $\omega_O$ . For example, a square wave of fundamental  $\omega_O/3$  will have a substantial component at  $\omega_{\mbox{\scriptsize O}}$  to which the loop can lock. Even a pure sine wave input signal can be used for harmonic locking if the PLL input stage is overdriven. (The resultant internal limiting generates harmonic frequencies.) Locking to even harmonics or subharmonics is the least satisfactory, since the input or VCO signal must contain second harmonic distortion. If locking to even harmonics is desired, the duty cycle of the input and VCO signals must be shifted away from the symmetrical to generate substantial Sheet 4U.com even harmonic, content.

et4U.com

DataSheet4U.com

et4U.com

# Modeling the PLL

**AN178**

In evaluating the loop for a potential application, it is best to actually compute the magnitude of the expected signal component nearest  $\omega_O$ . This magnitude can be used to estimate the capture and lock ranges.

All of Philips Semiconductors loops are stabilized against center frequency drift due to power supply variations. Both the 565 and the 567 are temperature-compensated over the entire military temperature range (-55 to +125°C). To benefit from this inherent stability, however, the designer must provide equally stable (or better) external components. For maximum cost effectiveness in some non-critical applications, the designer may wish to trade some stability for lower cost external components.

#### **GUIDELINES FOR LOCK RANGE CONTROL**

Two things limit the lock range. First, any VCO can swing only so far; if the input signal frequency goes beyond this limit, lock will be lost. Second, the voltage developed by the phase comparator is proportional to the product of both the phase and the amplitude of the in-band component to which the loop is locked. If the signal amplitude decreases, the phase difference between the signal and the VCO must increase in order to maintain the same output voltage and, hence, the same frequency deviation. The 564 contains an internal limiter circuit between the signal input and one input to the phase comparator. This circuit limits the amplitude of large input signals such as those from TTL outputs to approximately 100mV before they are applied to the phase comparator. The limiter significantly improves the AM rejection of the PLL for input signal amplitudes greater than 100mV.

This happens so often with low input amplitudes that even the full ±90° phase range of the phase comparator cannot generate enough voltage to allow tracking wide deviations. When this occurs, the effective lock range is reduced. Weak input signals cause a reduction of tracking capability and greater phase errors. Conversely, a strong input signal will allow the use of the entire VCO swing capability and keeps the VCO phase (referred to the input signal) very close to 90° throughout the range. Note that the lock range does not depend on the low-pass filter. However, if a low-pass filter is in the loop, it will have the effect of limiting the maximum rate at which tracking can occur. Obviously, the LPF capacitor voltage cannot change instantly, so lock may be lost when large enough step changes occur. Between the constant frequency input and the step-change frequency input is some limiting frequency slew rate at which lock is just barely maintained. When tracking at this rate, the phase difference is at its limit of 0° or 180°. It can be seen that if the LPF cutoff frequency is low, the loop will be unable to track as fast as if the LPF cutoff frequency is higher. Thus, when maximum tracking rate is needed, the LPF should have a high cutoff frequency. However, a high cutoff frequency LPF will attenuate the sum frequencies to a lesser extent so that the output contains a significant and often bothersome signal at twice the input frequency. The phase comparator's output contains both sum and difference frequencies. During lock, the difference frequency is zero, but the sum frequency of twice the locked frequency is still present. This sum frequency component can then be filtered out with an external low-pass filter.

#### INPUT LEVEL AMPLITUDE SELECTION

Whenever amplitude limiting of the in-band signal occurs, whether in the loop input stages or prior to the input, the lock and capture ranges become independent of signal amplitude.

Better noise and out-band signal immunity is achieved when the input levels are below the limiting threshold, since the input stage is in its linear region and the creation of cross-modulation components is reduced. Higher input levels will allow somewhat faster operation due to greater phase comparator gain and will result in a lock range which becomes constant with amplitude as the phase comparator gain becomes constant. Also, high input levels will result in a linear phase versus frequency characteristic.

#### **CAPTURE RANGE CONTROL**

There are two main reasons for making the low-pass filter time constant large. First, a large time constant provides an increased memory effect in the loop so that it remains at or near the operating frequency during momentary fading or loss of signal. Second, the large time constant integrates the phase comparator's output so that increased immunity to noise and out-band signals is obtained.

Besides the lower tracking rates attendant to large loop filters, other penalties must be paid for the benefits gained. The capture range is reduced and the capture transient becomes longer. Reduction of capture range occurs because the loop must utilize the magnitude of the difference frequency component at the phase comparator to drive the VCO towards the input frequency.

If the LPF cutoff frequency is low, the difference component amplitude is reduced and the loop cannot swing as far. Thus, the capture range is reduced.

## LOCK-UP TIME AND TRACKING SPEED CONTROL

In tracking applications, lock-up time is normally of little consequence, but occasions do arise when it is desirable to keep lock-up time short to minimize data loss when noise or extraneous signals drive the loop out of lock. Lock-up time is of great importance in tone decoder type applications. Tracking speed is important if the loop is used to demodulate an FM signal. Although the following discussion dwells largely on lock-up time, the same comments apply to tracking speeds.

No simple expression is available which adequately describes the acquisition or lock-up time. This may be appreciated when we review the following factors which influence lock-up time.

- a. Input phase

- b. Low-pass filter characteristic

- c. Loop damping

- d. Deviation of input frequency from center frequency

- e. In-band input amplitude

- f. Out-band signals and noise

- g. Center frequency

DataShe

DataSheet4U.com www.DataSheet4U.com

# Modeling the PLL

**AN178**

Fortunately, it is usually sufficient to know how to improve the lock-up time and what must be sacrificed to get faster lock-up. Consider an operational loop or tone decoder where occasionally the lock-up transient is too long. What can be done to improve the situation - keeping in mind the factors that influence lock?

Figure 13. Probability of Lock vs Input Cycles

- a. Initial phase relationship between incoming signal and VCO This is the greatest single factor influencing the lock time. If the from the input frequency so that the VCO frequency must walk back on the beat notes. Figure 13 gives a typical distribution of lock-up times with the input pulse initiated at random phase. The only way to overcome this variation is to send phase information all the time so that a favorable phase relationship is guaranteed at t = 0. For example, a number of PLLs or tone decoders may be weakly locked to low amplitude harmonics of a pulse train and the transmitted tone phase related to the same pulse train. Usually, however, the incoming phase cannot be controlled.

- b. Low-pass filter The larger the low-pass filter time constant, the longer will be the lock-up time. The lock-up time can be reduced by decreasing the filter time constant, but in doing so, some of the noise immunity and out-band signal rejection will be sacrificed. This is unfortunate, since this is what necessitated the use of a large filter in the first place. Also present will be a sum frequency (twice the VCO frequency) component at the low pass filter and greater phase jitter resulting from out-band signals and noise. In the case of the tone decoder (where control of the capture range is required since it specifies the device bandwidth) a lower value of low-pass capacitor automatically increases the bandwidth. Speed is gained only at the expense of added bandwidth.

- c. Loop damping A simple first-order lowpass filter of the form

$$F(s) = \frac{1}{1-s} \tag{66}$$

produces a loop damping of

$$= 1 2 \frac{1}{K_V}$$

(67)

Damping can be increased not only by reducing  $\pi$ , as discussed DataSheet4U.com, but also by reducing the loop gain K<sub>V</sub>. Using the loop

- gain reduction to control bandwidth or capture and lock ranges achieves better damping for narrow bandwidth operation. The penalty for this damping is that more phase comparator output is required for a given deviation so that phase errors are greater and noise immunity is reduced. Also, more input drive may be required for a given deviation.

- d. Input frequency deviation from free-running frequency Naturally, the further an applied input signal is from the free-running frequency of the loop, the longer it will take the loop to reach that frequency due to the charging time of the low-pass filter capacitor. Usually, however, the effect of this frequency deviation is small compared to the variation resulting from the initial phase uncertainty. Where loop damping is very low, however, it may be predominant.

- e. In-band input amplitude Since input amplitude is one factor in the phase comparator's gain K<sub>d</sub>, and since K<sub>d</sub> is a factor in the loop gain K<sub>v</sub> damping is also a function of input amplitude. When the input amplitude is low, the lock-up time may be limited by the rate at which the low-pass capacitor can charge with the reduced phase comparator output (see d above).

- f. Out-band signals and noise Low levels of extraneous signals and noise have little effect on the lock-up time, neither improving or degrading it. However, large levels may overdrive the loop input stage so that limiting occurs, at which point the in-band signal starts to be suppressed. The lower effective input level can cause the lock-up time to increase, as discussed in e above.

- terms of the number of cycles to lock, fastest lock-up is achieved at higher frequencies. Thus, whenever a system can be operated at a higher frequency, lock will typically take place faster. Also, in systems where different frequencies are being detected, the higher frequencies, on the average, will be detected before the lower frequencies.

However, because of the wide variation due to initial phase, the reverse may be true for any single trial.

## PLL MEASUREMENT TECHNIQUES

This section deals with measurements of PLL operation. The techniques suggested are meant to help the designer in evaluating the performance of the PLL during the initial setup period as well as to point out some pitfalls that may obscure loop evaluation. Recognizing that the test equipment may be limited, techniques are described which require a minimum of standard test items.

The majority of the PLL tests described can be done with a signal generator, a scope and a frequency counter. Most laboratories have these. A low cost digital voltmeter will facilitate accurate measurement of the VCO conversion gain. Where the need for a FM generator arises, it may be met in most cases by the VCO of a Philips Semiconductors PLL. Any of the loops may be set up to operate as a VCO by simply applying the modulating voltage to the low-pass filter terminal(s). The resulting generator may be checked for linearity by using the counter to check frequency as a function of modulating voltage. Since the VCOs may be modulated right down to DC, the calibration may be done in steps. Moreover, loop measurements may be made by applying a constant frequency to the loop input and the modulating signal to the low-pass filter terminal to simulate the effect of a FM input so that an FM generator may be omitted for many measurements. www.DataSheet4U.com

DataShe

# Modeling the PLL

**AN178**

DataShe

#### FREE-RUNNING FREQUENCY

Free-running frequency measurements are easily made by connecting a frequency counter or oscilloscope to the VCO output of the loop. The loop should be connected in its final configuration with the chosen values of input, bypass, and low-pass filter capacitors. No input signal should be present. As the free-running frequency is read out, it can be adjusted to the desired value by the adjustment means selected for the particular loop. It is important not to make the frequency measurement directly at the timing capacitor, unless the capacity added by the measurement probe is much less than the timing capacitor value, since the probe capacity will then cause a frequency error.

When the frequency measurement is to be converted to a DC voltage for production readout or automated testing, a calibrated phase-locked loop can be used as a frequency meter.

## **CAPTURE AND LOCK RANGES**

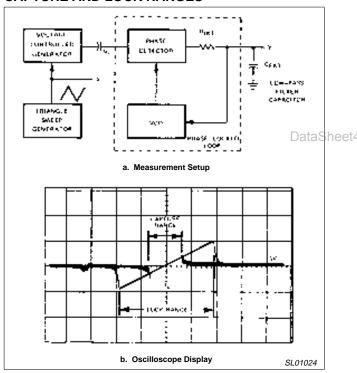

Figure 14. Capture and Lock Ranges

Figure 14a shows a typical measurement setup for capture and lock range measurements. The signal input from a variable frequency oscillator is swept linearly through the frequency range of interest and the loop FM output is displayed on a scope or (at low frequencies) X-Y recorder. The sweep voltage is applied to the X axis.

Figure 14b shows the type of trace which results. The lock range is given by the outer lines on the trace, which are formed as the incoming frequency sweeps away from the center frequency. The inner trace, formed as the frequency sweeps toward the center frequency, designates the capture range. Linearity of the VCO is revealed by the straightness of the trace portion within the lock range. The slope  $(\Delta f/\Delta V)$  is the conversion gain  $K_0$  for the VCO at the particular free-running frequency.

By using the sweep technique, the effect on free-running frequency, capture range, and lock range of the input amplitude, supply voltage, low-pass filter and temperature can be examined.

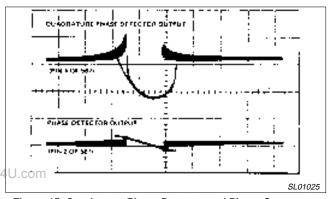

Because of the lock-up time duration and variation, the sweep frequency must be much lower than the free-running frequency, especially when the capture range is below 10% of the free-running frequency. Otherwise, the apparent capture and lock range will be functions of sweep frequency. It is best to start sweeping as slowly as possible and, if desired, increase the rate until the capture range begins to show an apparent reduction — indicating that the sweep is too fast. Typical sweep frequencies are in the range of 1/1000 to 1/100,000 of the free-running frequency. In the case of the 567, the quadrature detector output may be similarly displayed on the Y axis, as shown in Figure 15, showing the output level versus frequency for one value of input amplitude.

Figure 15. Quadrature-Phase Detector and Phase Comparator Outputs of the NE567 PLL

Capture and lock range measurements may also be made by sweeping the generator manually through the band of interest. Sweeping must be done very slowly as the edges of the capture range are approached (sweeping toward center frequency) or the lock-up transient delay will cause an error in reading the band edge. Frequency should be read from the generator rather than the loop VCO because the VCO frequency gyrates wildly around the center frequency just before and after lock. Lock and unlock can be readily detected by simultaneously monitoring the input and VCO signals, the DC voltage at the low-pass filter, or the AC beat frequency components at the low-pass filter. The latter are greatly reduced during lock as opposed to frequencies just outside of lock.

## FM AND AM DEMODULATION DISTORTION

These measurements are quite straight-forward. The loop is simply set up for FM detection and the test signal is applied to the input. A spectrum analyzer or distortion analyzer (HP333A) can be used to measure distortion at the FM output.

For FM demodulation, the input signal amplitude must be large enough so that lock is not lost at the frequency extremes. The data sheets give the lock (or tracking) range as a function of input signal and the optional range control adjustments. Due to the inherent linearity of the VCOs, it makes little difference whether the FM carrier is at the free-running frequency or offset slightly as long as the tracking range limits are not exceeded.

The faster the FM modulation in relation to the center frequency, the lower the value of the capacitor in the low pass filter must be for

et4U.com

DataSheet

DataSheet4U.com

# Modeling the PLL

**AN178**

satisfactory tracking. As this value decreases, however, it attenuates the sum frequency component of the phase comparator output less. The demodulated signal will appear to have greater distortion unless this component is filtered out before the distortion is measured.

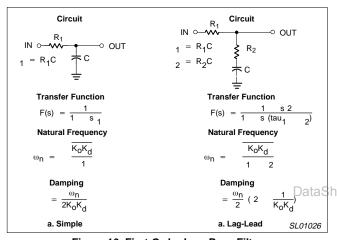

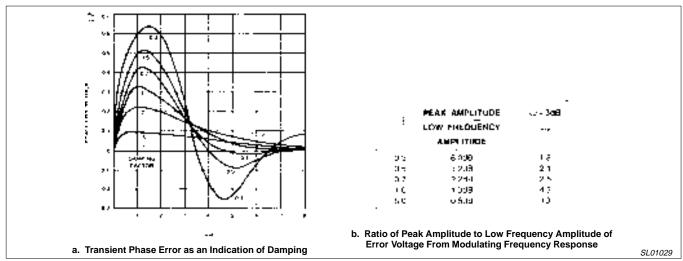

#### NATURAL FREQUENCY AND DAMPING

Circuits and mathematical expressions for the natural frequencies and dampings are given in Figure 16 for two first-order low-pass filters. Because of the integrator action of the PLL in converting frequency to phase, the order of the loop always will be one greater than the order of the LPF. Hence, both these first-order LPFs produce a second-order PLL system.

Figure 16. First-Order Low-Pass Filters

The natural frequency  $(\omega_n)$  of a loop in its final circuit configuration can be measured by applying a frequency-modulated signal of the desired amplitude to the loop. Figure 16 shows that the natural frequency is a function of  $K_d$ , which is, in turn, a function of input amplitude. As the modulation frequency  $(\omega_m)$  is increased, the phase relationship between the modulation and recovered sine wave will go through  $90^\circ$  at  $\omega_m=\omega_n$  and the output amplitude will peak.

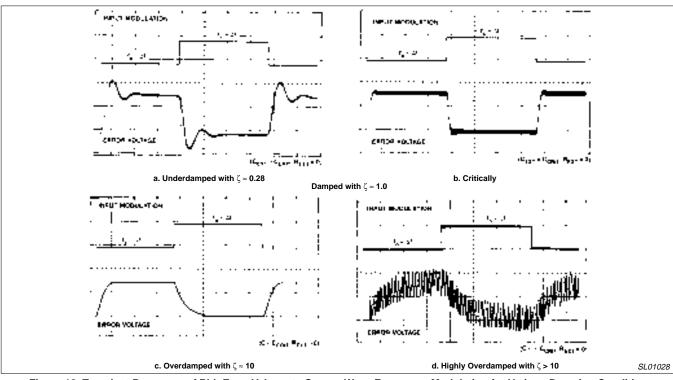

Figure 17. Measurement Setup for Display of PLL Transient Response

Damping is a function of  $K_d$ ,  $K_o$ , and the lowpass filter. Since  $K_o$  and  $K_d$  are functions of the free-running frequency and input amplitude, respectively, damping is highly dependent on the particular operating condition of the loop. Damping estimates for the desired operating condition can be made by applying an input signal which is frequency-modulated within the lock range by a square wave. The low-pass filter voltage is then monitored on an oscilloscope which is synchronized to the modulating waveform, as shown in Figure 17. Figure 18 shows typical waveforms displayed. The loop damping can be estimated by comparing the number and magnitude of the overshoots with the graph of Figure 19, which gives the transient phase error due to a step in input frequency.

An expression for calculating the damping for any underdamped second-order system ( $\zeta$  < 1.0) when the normalized peak overshoot is known is

$$M_p = 1 e^{-1/2}$$

(68)

Examination of Figure 18 shows that the normalized peak overshoot of the error voltage is approximately 1.4. Using this value for  $M_p$  in Equation 68 gives a damping of  $\zeta \approx 0.28$ .

Another way of estimating damping is to make use of the frequency response plot measured for the natural frequency  $(\omega_n)$  measurement. For low damping constants, the frequency response measurement peak will be a strong function of damping. For high damping constants, the 3dB down point will give the damping. Figure 19 tabulates some approximate relationships.

DataShe

www.DataSheet4U.com

ataSheet4U.com

et4U.com

1988 Dec

# Modeling the PLL

**AN178**

Figure 18. Transient Response of PLL Error Voltage to Square Wave Frequency Modulation for Various Damping Conditions

Figure 19. Estimating the Damping in a Second-Order PLL

## **NOISE**

et4U.com

The effect of input noise on loop operation is very difficult to predict. Briefly, the input noise components near the center frequency are converted to phase noise. When the phase noise becomes so great that the +905 permissible phse variation is exceeded, the loop drops out of lock or fails to acquire lock. The best techniques is to actually apply the anticipated noise amplitude and badwidth to the input and then perform the capture and lock range measurements as well as perform operating tests with the anticipated input level and modulation deviations. By including a small safety factor in the loop DataSheet design to compensate for small processing variations, satisfactory operation can be assured.

www.DataSheet4U.com

DataShe

1988 Dec DataSheet 4 U .com

Modeling the PLL

**AN178**

**NOTES**

et4U.com

DataSheet4U.com

DataShee

DataSheet4U.com www.DataSheet4U.com

# Modeling the PLL

**AN178**

et4U.com

## DataSheet4U.com

Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 Philips Semiconductors and Philips Electronics North America Corporation register eligible circuits under the Semiconductor Chip Protection Act.

© Copyright Philips Electronics North America Corporation 1988

All rights reserved. Printed in U.S.A.

Let's make things better.

DataSheet4U.com

Philips Semiconductors